EPSON石英晶體諧振器電路設計暨測試驗證介紹-下篇

EPSON石英晶體諧振器電路設計暨測試驗證介紹-下篇

文: 邱秉毅,服務於台灣愛普生科技股份有限公司,電子零件事業部

振盪器設計於電路中,其最重要的項目為提供系統所需頻率,但系統對於頻率精準度有其最大規格上、下限需求,相關規格需求將視所選用搭配系統晶片和產品會有不同要求,例如Wi-Fi (IEEE 802.11) ≤ ±20ppm、Bluetooth (IEEE 802.15) ≤ ±40ppm、Ethernet (IEEE 802.3) ≤ ±50ppm等,

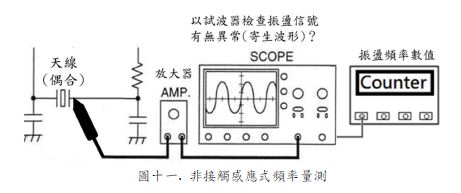

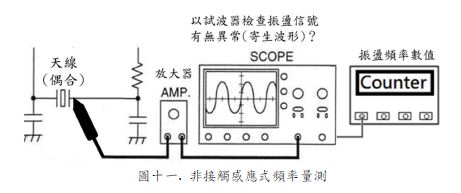

當要量測使用石英晶體自行設計石英振盪電路實際頻率量測方法,愛普生實驗室是採用改造於主動探棒來當偶合用信號天線,再結合信號放大器,將電路板上的振盪信號以非接觸式偶合方法來量測信號頻率,信號先接入試波器後,再輸出給計頻器。

我們以非接觸式偶合感應其振盪頻率信號,所量測得到的頻率精準度非常可靠,它不會因為主動探棒直接碰觸振盪電路某點,振盪電路頻率將會因來自主動探棒本體電容和容抗值,影響到振盪電路實際負載電容量,造成真實振盪頻率因為量測頻率方法不佳造成的頻率量測偏差。圖十一,為愛普生量測石英晶體在振盪電路上產生頻率的方法,試波器是讓我們用來檢驗待量測指定的振盪信號波形是否異常?是否會觀察到來自電路中電源雜訊,或是有異常信號來自不同層走線所偶合來的寄生波形,或其它雜訊來源?

如果待量測振盪電路信號本身品質沒有問題,將會用計頻測讀取振盪頻率數值。

石英晶體定義頻率精準規格為數值範圍,故被量測電路上的石英晶體自身偏差數值,將會影響被量測盪電路的頻率偏移特性的觀察。在輸出頻率評估時,主要是以頻率偏差值進行判斷,其頻率偏差值(Frequency deviation)計算方式為下,

[ (振盪電路量測之輸出頻率) - (石英晶體自身頻率) ∕ 額定頻率值 ] x 106

通常判斷振盪電路頻率偏差量標準,以高頻AT-Cut MHz*石英元件來說,室溫檢查量測時預設頻率偏差量,約接近0ppm越好(通常,我們會忽略正偏或負偏)。但是否精準的同時,必需要兼顧負性阻抗和驅動功率是否符合設計條件。

*使用於計時器用32.768kHz音叉式石英元件,預設頻率偏差最好常保持正偏差。

【第五部】振盪電路頻率(F)、負性阻抗(-R)、驅動功率(Drive Level)間相互關連

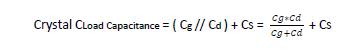

引響振盪線路頻率精準度或穩定與否,重要的參數就是整個線路上的負載電容CL (Load Capacitance),它是由Gate端的頻率調整電容(Cg)和Drain端的頻率調整電容(Cd)及PCB走線和IC內部整體雜散電容(CStray)等三個變數共同組成。

其中Crystal負載電容及兩個落地電容為已知的參數,我們可以透過下列公式概略求得雜散電容值:

初版PCB電路設計,我們可依上公式,振盪電路中未知的Cstray偏差值,以2 ~ 3pF數值先「暫時」代入,便可概略推算出所需外掛於Cg 和Cd端的電容值,初步設計時,我們通常只需設定Cg=Cd兩端外掛相互等同電容數值便可。

(例)當選用石英元件CLoad = 12.5pF時,我們將CStray ≈ 2 ~ 3pF暫代入推算在此,可計算得到Cg = Cd = 18pF ~ 22pF為概略建議範圍,相關MLCC電容數值挑選,請依貴司常使用MLCC標準零件值來決定。

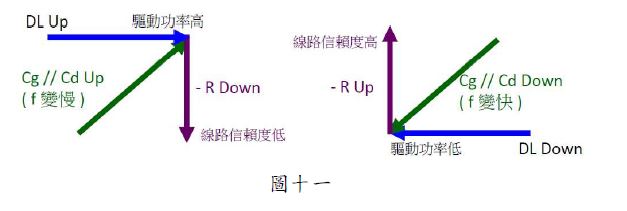

[ 5-1 ] 當外掛電容Cg//Cd增加時,其輸出頻率變慢、負性阻抗(-R)降低;相反,如外掛電容Cg//Cd降低時,其輸出頻率變快、負性阻抗(-R)增加。

如下圖十一所示:

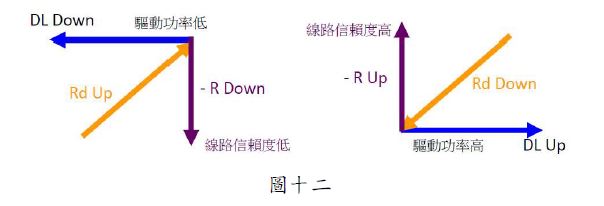

[ 5-2 ] 關於限流電阻(Rd)調整,主要的目的為降低驅動功率,讓使用的石英晶體在振盪電路的特性能夠常保持穩定條件;隨著外掛電容調整可達高精準度,但驅動功率亦會隨之變動,故需藉由限流電阻(Rd),進行調整達其目的。

當限流電阻增加時,驅動功率、負性阻抗兩者皆降低;相反,當限流電阻不用或是將其降低時,驅動功率、負性阻抗兩者隨之增加(參閱圖十二)。此限流電阻於電路設計時,如有預留,可調整搭配主晶片設計驅動功率過大時,可藉由此Rd進行微調,相反如無使用可以零歐姆電阻代之。

由於增加限流電阻有其極限,無法無限增加,故需取得各參數平衡。

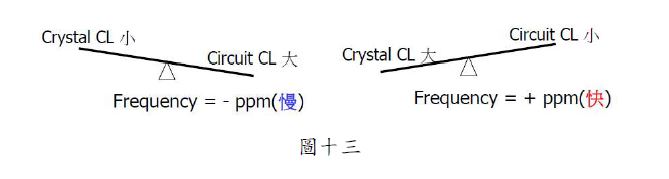

[5-3] 當選用石英晶體選用的CLoad低於實際振盪電路的CLoad時,依此條件匹配下所量得輸出頻率會變較慢(負偏差),如需取得精準輸出頻率,需將電路中的兩外掛Cg、Cd電容漸次調小,達成相互匹配平衡;反之,當選用石英晶體選用的CLoad高於實際振盪電路的CLoad時,依此條件匹配下所量得輸出頻率會變較快(正偏差),如需取得精準輸出頻率,需將電路中的兩外掛電容調大,達成平衡。參考下圖十三所示:

本篇為愛普生石英晶體諧振器電路設計暨測試驗證相關介紹說明的下篇,全文版本我們將會另行發行。石英晶體元件是電子業界性價比高的被動元件,它廣泛被設計使用於各類電子產品半導體所需要的高精度時脈來源,石英晶體雖然便宜且性價比高,但是以它用來設計出的石英振盪電路是類比電路,設計者很難去驗證測試所設計的振盪電路參數正常與否?

如果您有任何石英振盪電路設計問題,或有相關工程驗證需求,歡迎隨時和台灣愛普生聯絡,或透過各授權代理商洽詢相關測試服務支援。

有關精工愛普生公司相關連結: Notes for Oscillator circuit design - YouTube

如有興趣,歡迎聯絡我們。 社群連結:YouTube | Facebook | Twitter