EPSON 石英晶體諧振器電路設計暨測試驗證介紹(上篇)

EPSON石英晶體諧振器電路設計暨測試驗證介紹(上篇)

文: 邱秉毅,服務於台灣愛普生科技股份有限公司,電子零件事業部

選擇高品質石英晶體諧振器指標

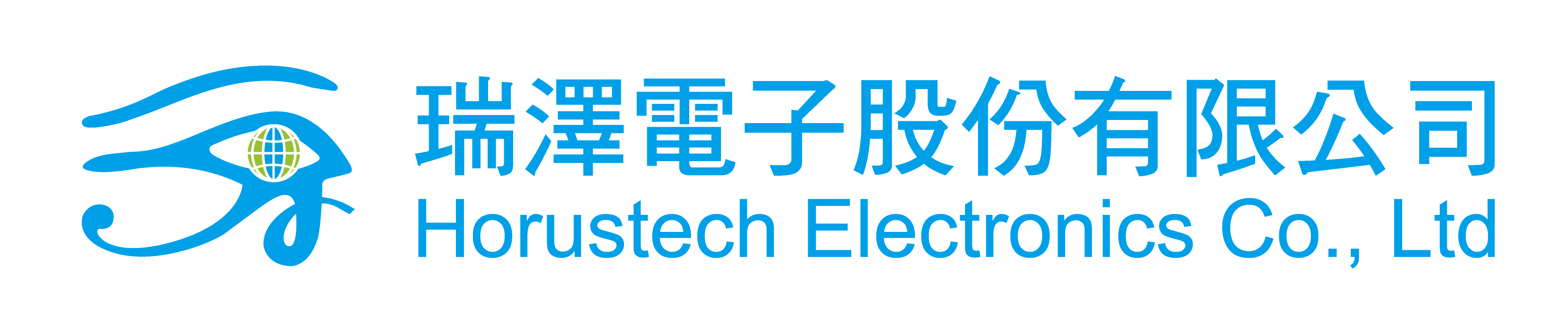

傳統石英晶體諧振器(下稱石英元件)是電子產品中不可或缺的頻率控制元件,可產生及穩定電子電路所需的工作頻率,因應目前資訊、通訊產業、車用、工業控制的各類應用產品,更是無法取代的頻率穩定元件。一般使用者來說,選擇石英元件以成本考量為第一要件,但本文並非鼓勵以此項為首要條件,建議以市場主流尺寸、晶片設計方式、電極面設計導電材料(鍍金)、頻率穩定度與可靠度為主(參閱下圖一. 石英元件等效電路暨相關參數名),取得高品質石英元件後,依照搭配主晶片選擇適合石英晶振負載電容值,再進行振盪電路迴路匹配調整其頻率精準度、驅動功率、負性阻抗特性,並符合整體系統搭配應用。其相關內容如下:

圖一. 石英元件等效電路

石英振盪器電路周邊所需元器件和功能說明石英振盪器設計電路種類非常多元,當振盪電路設計不當時,容易產生振盪電路不穩定或異常等情況,故在進行振盪電路設計時,必須事前評估整體相關電路和周邊元器件特性選擇是否符合適正設計規範。

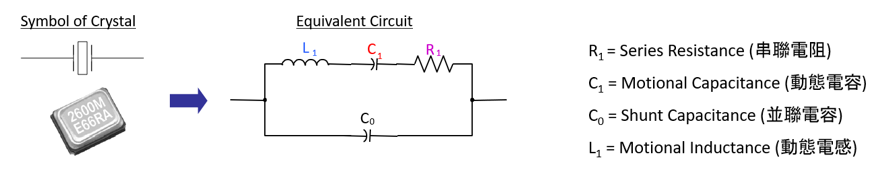

目前最常見設計為考畢斯振盪電路(參閱圖二),其電路本身的電子元器件需求最精簡、穩定性高、周邊所需電子元器件取得方便,常運用在石英振盪電路設計上。

我們先簡單說明其周邊元器件功能,

1.Rf (Feed Back Resistance-迴授電阻):為振盪電路必要設計元件,其目的是用於反向器增益放大信號用,無此迴授電阻時,振盪電路無法運作,通常設計分為以下兩種,

一.已預建於搭配主晶片內振盪電路中,請勿再外掛該迴授電阻於外部電路,

二.未預建於搭配主晶片內振盪電路中,需要將該迴授電阻設計於外部電路,其中設計於外部電路,會依需設計振盪頻率之不同,選擇不同的迴授電阻阻值,32.768KHz (音叉式石英)迴授電阻 - 常選擇10M ~ 20MΩ設計阻值。高頻MHz (AT Cut X’TAL)迴授電阻 - 常選擇1MΩ設計阻值。

2.Rd (Drain Resistance-限流電阻) :為諧振電路串聯的電阻,設計於XTAL_OUT端,其主要目的為降低振盪迴路中流過石英元件的驅動電流,藉由達到降低驅動功率(Drive Level)效果、防止異常振盪(不穩定頻率跳動),並降低靜噪目的。

3.Cg、Cd (Gate、Drain Capacitance-分外掛於閘級和汲極兩端負載電容):主要目的為調整輸出頻率精準度,如果兩負載電容值過大或不足,皆會造成振盪電路穩定性發生問題(甚至因為振盪電路無法起振輸出適正時脈信號,造成電路或系統無法開機運作),此部分調整影響頻率精準度同時,石英振盪電路相關重要參數和特性(負性阻抗、驅動功率等)亦將會隨之變化影響。 圖二. 考畢斯振盪電路

圖二. 考畢斯振盪電路

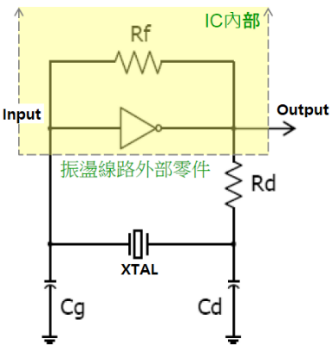

當了解各周邊元器件和其功能後,需進一步評估整體振盪電路參數特性,是否滿足電路系統所需,如下三項指標為評估振盪電路穩定與否最主要參數,

1.振盪設計額定輸出頻率偏差?關於振盪電路輸出頻率偏差主要為石英元件單體偏差值,與實際輸出頻率兩者的偏差值,即可推估出實際可用的頻率範圍;

2.振盪最大阻抗餘裕量(或稱振盪裕度)?振盪最大阻抗餘裕量其主要是評估觀察,選擇的石英元件在特定電路下,觀察該電路起振最大裕度是否能夠達成該石英元件其規格之最大等效電阻值

(Equivalent Series Resistance),通常以其最大ESR電阻值再乘上5倍,為判斷基準(滿足的倍數越高,代表該特定振盪電路條件下,達到更優異的安定性)

驅動功率主要是評估觀察主IC提供給石英元件的實際驅動功率,利用量測流經該石英元件實際電流值,將其平方後,再乘上該被測物料該石英元件實際內部等效電阻值,依P = i2 x R公式來計算實際驅動功率。

當以上三項脩關振盪電路穩定與否最重要指標,取得平衡(如圖三所示),代表該石英元件搭配主IC和其周邊元器件,包含其外掛於閘極端(XTAL_IN)和汲

極端(XTAL_OUT)所需選用電容值等,為振盪電路適正設計參數,此為測試主要目的。

圖三. 電器特性平衡區

本篇為本系列上篇,下一篇我們將會詳細介紹說明如何觀察各項重要指標的測試方法,請期待本系列中篇說明。

有關精工愛普生公司介紹相關連結:Notes for Oscillator circuit design - YouTube

如有興趣,歡迎聯絡我們。社群連結:YouTube | Facebook | Twitter