愛普生 - 通信系统所需信號品質與標準訊號源介紹〔上篇〕

.png)

通信系统所需信號品質與標準訊號源[上篇]

資訊參考來源:

https://www.epson.com.cn/Apps/ed/Crystal/pdf/technology_12.pdf

Epson 技術介紹

AN0028 ( May, 2022 )

文: 邱秉毅,服務於台灣愛普生科技股份有限公司 電子零件事業部。

標準信號源所需振盪器的關鍵規格與產品介紹

通信傳輸網路的世界中,核心網路、區域網路、傳輸網路、接入網和企業網路(LAN/SAN) 從上至 下呈樹狀分布。每種網路均設定了各自通信所需的規格。而且,伴隨近年高速通信终端及影像傳輸等普及,核心網路中流過的通信量有增無減,通信的高速、大容量化進展迅速,通信基礎設備亦不 斷擴充。進行如上所示的高速網路通信的通信協議所需要具備傳輸線路、系统以及錯誤率等性能。 錯誤率(Bit Error Rate 簡稱稱為“BER”)是指進行接收、發射訊號之際,接收端接收到數據中的錯誤數 除以發出的數據總結數得出的錯誤率。尤其對於對 BER,信號所具有的 Noise 和 Jitter 是非常重要的 參數,對訊號的品質的影響極大。本次,我們將說明基於通信設備所需的訊號品質而要求振盪具備的關鍵規格,介绍市場中的振盪器結構與特性,以及適合應用於訊號設備的愛普生產品。

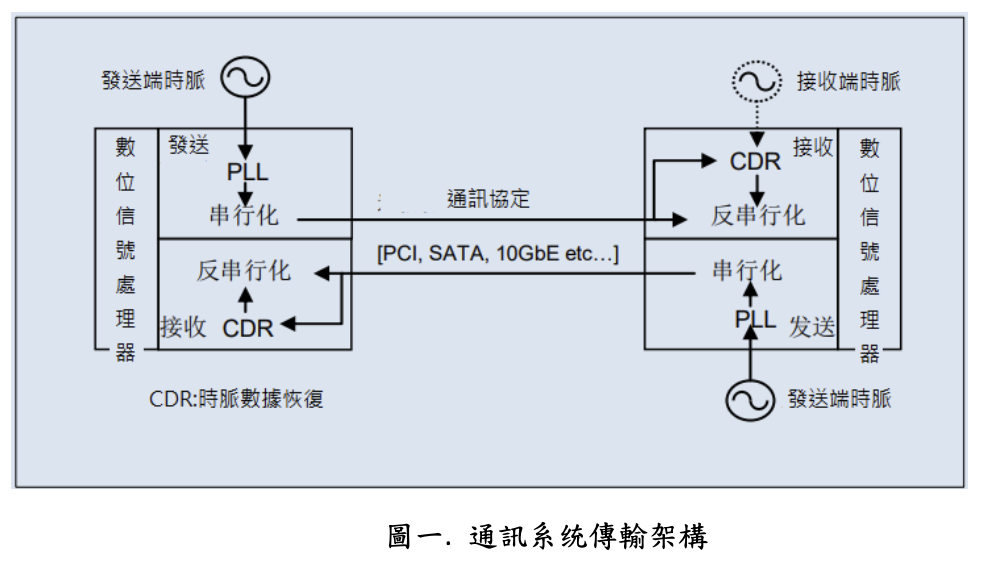

【高速通信系统的架構】

首先,參考圖一所式,表示發射端、接收端之間通過 PCI、SATA 或 10GbE 等各種通訊協定,傳 輸數據通常採用通訊系统傳輸架構進行。在這樣的系統中,使用振盪器產生一個標準訊號源。通 常,標準訊號源採用低於數據傳輸率的频率源時脈。所以,為了以標準訊號源產生串聯數據,發送 端採用發射機與接收機之中的鎖相迴路(PLL,Phase Locked Loop)把標準訊號源的頻率倍增到需要的 频率後發送出去。

與此相對,接收端使用接收到的數據傳入鎖相迴路的時脈數據(Clock Data Recovery)還原標準訊 號源,並採用還原後標準訊號源數據。在部分高端系统中,也採用根據接收端所持有的標準訊號源數據的方式。如上所示,在發射端、接收端的過程中隨時進行訊號的轉換與還原。在日益高速的通信中,接收端必须正確判斷接收的數據是 0 或是 1。

因此,如何抑制訊號本身的抖動(Jitter)和噪音(Noise),並提高訊號品質,如何設計最佳的傳輸線 路專用集成電路是非常重要的課題。

【訊號品質評估方式】

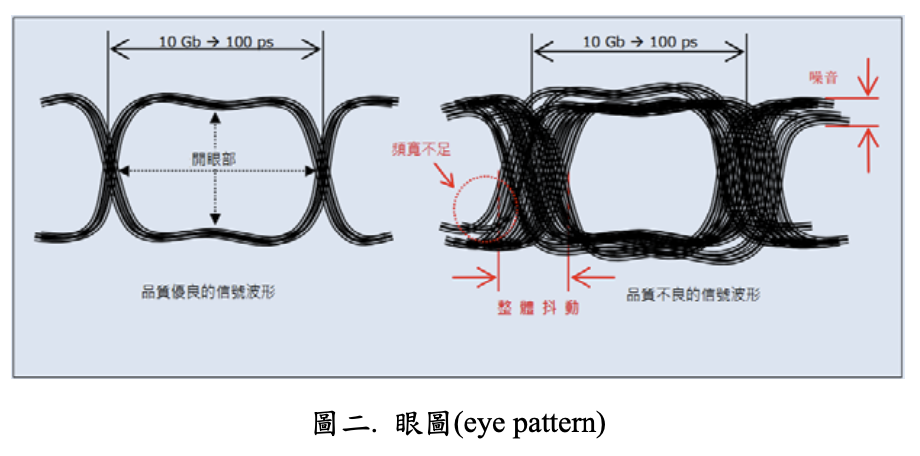

評估通信系统中訊號本身的品質時,經常使用眼圖(eye pattern)進行評估。眼圖是使用高階示波器 等測試儀器擷取收集大量高速數據信號波形後重合而成的圖形,由於波形重合後呈“眼”狀而稱之為 眼圖。

假設傳輸線路的通信協定為 10GbE,該系统中傳輸 10Gbps 的信號所用時間(長度)為各週期 100 皮秒。評估信號品質時,將每隔 100 皮秒重複出現的信號相互重合後製成眼圖。假設標準訊號很纯 正且傳輸線路的專用集成電路設計良好,則可獲得如下圖二左所示的幾乎完全重合的波形。

與其相反,如果標準信號中噪音(Noise)和抖動(Jitter)較多或因專用集成電路的設計而產生傳輸線 路的頻寬不足 等損失,信號波形則會變得不穩定,重合後的波形呈現圖二右所示的眼圖逐漸閉攏的 情况。

判斷信號數據是 0 還是 1 時,重要的是其眼部開口長寬空間及裕度需滿足系統運行要求。開眼部因噪音和抖動而縮小,將導致接收端無法準確判斷信號數據,BER 變高。現在幾乎所有通信系統均要求 BER 至少應達到 1x10 ̅¹²。這意味著每傳輸 10¹²週期的數據時允許出現一個週期的錯誤。综上所述,從眼圖中可以獲得噪音、抖動或频寬不足等有關信號品質的各種信息。

【構成抖動的要素】

參考圖三,表示通信系统中抖動的構成要素。總體抖動 TJ (Total Jitter)用確定性抖動 DJ (Deterministic Jitter)與隨機抖動 RJ (Random Jitter) 之和來表示。

確定性抖動(DJ),表示因電路設計、電磁感應或外界因素而產生的抖動。

確定性抖動的特性是频率擴散保持一定,且與時間變化無關。作為標準訊號源的振盪器性能中影響確定性抖動的是失真和諧波。

隨機抖動(RJ),名副其實表示無法預測的抖動成份。它受元件本身的特性、熱噪音等因素的影響 而自然產生。

隨機抖動的特性是隨時間随而擴散。作為標準訊號源的振盪器性能中,影響隨機抖動的正是標準 訊號源的抖動。其它系统中的因素也被歸類為產生抖動的要因,例如:插件的電源噪音與串擾、因 電纜設計等影響而引起的频寬不足是產生確定性抖動的要因,而專用集成電路的噪音等則是產生隨 時抖動的要因。因此,系统設計人員需要通過改善專用集成電路的設計、變更基板布局(Layout)以及 變更部品等减小總體抖動。

【常見振盪器設計結構與種類】

目前市場中的振盪器大致可分為四種類型,其設計基礎架構如下圖四所示:

第一類,是最為常見的基本波起振的振盪器(A T-XO),

這類振盪器的噪音、抖動及失真特性十分優越,能提供高精度和高性能的所有特性。它的電路組成也相對簡單,所以能夠把耗電量控制在較小程度。

第二類,利用三次諧振波振盪器(3rd OverTone-XO),

諧波起振的電路設計中所採用的方法是利用濾波電路壓抑基本波訊號,使搭配 IC 取得三次諧波訊號。這種方法也存在著耗电量增加,以及電容比增大而使频率可變幅度變小的缺点。

第三類,利用鎖相迴路電路的振盪器(PLL-XO),

這類振盪器把石英作為標準訊號源提供輸入信號,再利用鎖相迴路電路生成輸入信号的同步信號,輸出必要的頻率。因此,這種方法的優點在於利用鎖相迴路電路技術獲任意頻率的便利性以及能够提供高频之處。但是,它的電路結構較為複雜致使耗电量增加,對噪音及抖動性能也带來了不

良影響。

良影響。

第四類,利用 LC 振盪器(LC-XO),

這類振盪器與鎖相迴路電路一樣即為方便,施加功率後輸出較大的振幅,且本身噪音也較低。與 此相反,由於材料本身所具有的 Q 值較低,所以频率穩定度和老化特性較差,低接近載波相位噪音 性也存在著問题。

【愛普生低相位抖動振盪器】

愛普生多採用基本波為旗下石英晶體振盪器產品線信號源為主要的產品設計,已形成了具備高速通信系统所需極低抖動性能特性的多款產品陣容。

我們主要原則為使用石英晶體元件作為頻率源。基本上頻率低於 80MHz 的石英晶體振盪器使用 AT 型石英晶體設計方式,80MHz 以上則使用了採用 AT 型的石英晶體的高頻基本波模式(High Frequency Fundamental,HFF) 技術,使用於多款高階石英振盪器,或多用於 JESD-2041 標準所需要 的高階極低抖動電壓控制石英晶體振盪器,具有最佳抖動性能的 LV-PECL、LVDS、HCSL 等各種 輸出模式,全部產品均保持了石英元件本身所獨特的優点,充分滿足各種電子產品應用規格需求。

以上為本篇為通信系统所需信號品質與標準訊號源,[上]、[下]兩部中的上篇,如有任何設計問題 時,可洽詢台灣愛普生公司各授權電子零件代理商,或是與我們聯絡。

更多有關 Epson 石英振盪器產品資訊,請參考

https://www5.epsondevice.com/en/products/crystal_oscillator/#sub02

更多有關 Epson 石英元件產品相關影片,請參考,

https://www5.epsondevice.com/en/information/technical_info/video/others.html

有關精工愛普生公司介紹相關連結 : global.epson.com/

如有興趣,歡迎聯絡我們

社群連結:YouTube | Facebook | Twitter